Memoria volatilis dynamica

Memoria volatilis dynamica vel vehemens[2] est genus memoriae volatilis quae quodque datorum bit in condensatro separato intra circuitum integratum reponit. Condensatrum electrice aut onerari aut non onerari potest; qui bini status binas aestimationes unius bit repraesentare habentur, usitate 0 et 1 appellatas. Quia transistra quae non conducunt parvam summam paulatim amittunt, condensatra energiam lente liberare solent, et data denique evanescunt nisi onus condensatri interdum redintegratur. Quia redintegratio necessaria est, haec memoria est dynamica, contra memoriam volatilem staticam et alia statica memoriae genera. Memoria volatilis dynamica, memoriae fulgureae dissimile, est volatilis (contra memoriam non volatilem), quia data cito amittit cum electricitas tollatur; memoria autem volatilis dynamica certam datorum remanentiam monstrat.

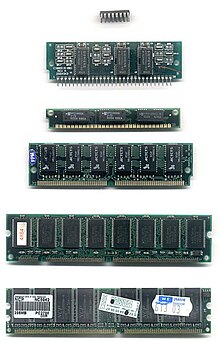

Memoria volatilis dynamica late in electronica digitali adhiberi solet, ubi memoriae vilis capacissimaeque opus est. Una e maximis memoriae volatilis dynamicae adhibitionibus in computatris hodiernis est memoria principalis (sermone humili RAM appellata).

Nexus interni

Notae

recensere- ↑ "How to "open" microchip and what's inside? : ZeptoBars". 15 Novembris 2012

- ↑ Anglice: dynamic random-access memory, DRAM.

Bibliographia

recensere- Jacob, Bruce, Spencer W. Ng, et David T. Wang. 2008. Memory Systems: Cache, DRAM, Disk. Morgan Kaufmann Publishers.

- Keeth, Brent, R. Jacob Baker, Brian Johnson, et Feng Lin. 2008. DRAM Circuit Design: Fundamental and High-Speed Topics. John Wiley & Sons. ISBN 0470184752. ISBN 9780470184752.

- Siddiqi, Muzaffer A. 2013. Dynamic RAM : technology advancements. Boca Raton Floridae: Taylor & Francis. ISBN 9781439893739.

Nexus externi

recensere- 1980. DRAM density and speed trends.

- 1997. Benefits of Chipkill-Correct ECC for PC Server Main Memory.

- 1994. Tezzaron Semiconductor Soft Error White Paper.

- Ars Technica. RAM Guide.

- Drepper, Ulrich. What every programmer should know about memory.

- Johnston, A. 2000. Scaling and Technology Issues for Soft Error Rates Stanford University.

- Mandelman, J. A., R. H. Dennard, G. B. Bronner, J. K. DeBrosse, R. Divakaruni, Y. Li, et C. J. Radens. 2002. Challenges and future directions for the scaling of dynamic random-access memory (DRAM). IBM.

- Patterson, David. Multi-port Cache DRAM—MP-RAM.

- Wang, David Tawei. 2005. Modern DRAM Memory Systems: Performance Analysis and a High Performance, Power-Constrained DRAM-Scheduling Algorithm. Diss. Ph.D. Collegium Universitatis Terrae Mariae. PDF.